# CHAPTER 3 LOGIC GATES

#### 3.1 Introduction

Circuits used to process digital signals are called Logic gates. Logic gates operates with binary numbers. All voltages used with Logic gates will be either "High" or "Low". In positive Logic, a High voltage means binary digits "1", while a Low voltage means binary digits "0". All digital systems are constructed using these Logic gates. Logic symbols are used to identify these circuits.

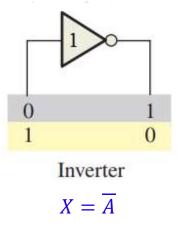

# 3.2 NOT (Inverter) gate

The inverter (NOT circuit) performs the operation called inversion or complementation. The inverter changes one logic level to the opposite level. In terms of bits, it changes a "1" to a "0" and a "0" to a "1".

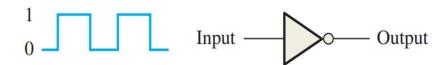

Example: A waveform is applied to an inverter in following figure. Determine the output waveform corresponding to the input and show the timing diagram. According to the placement of the bubble, what is the active output state?

#### Sol.

The output waveform is exactly opposite to the input (inverted), as shown in following figure, which is the basic timing diagram. The active or asserted output state is 0.

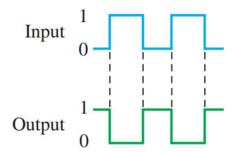

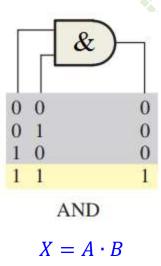

#### 3.3 The AND Gate

The AND gate is one of the basic gates that can be combined to form any logic function. An AND gate can have two or more inputs and performs what is known as logical multiplication.

The total number of possible combinations of binary inputs to a gate is determined by the following formula:

$$N=2^n$$

Where:

N is the number of possible input combinations.

n is the number of input variables.

Example: (a) Develop the truth table for a 3-input AND gate. (b) Determine the total number of possible input combinations for a 4-input AND gate.

#### Sol.

a) There are eight possible input combinations ( $2^3 = 8$ ) for a 3-input AND gate. The input side of the truth table shows all eight combinations of three bits. The output side is all 0s except when all three input bits are 1s.

|   | Inputs           | Output           |   |

|---|------------------|------------------|---|

| A | $\boldsymbol{B}$ | $\boldsymbol{C}$ | X |

| 0 | 0                | 0                | 0 |

| 0 | O                | 1                | O |

| 0 | 1                | 0                | O |

| O | 1                | 1                | O |

| 1 | O                | 0                | O |

| 1 | O                | 1                | O |

| 1 | 1                | O                | O |

| 1 | 1                | 1                | 1 |

b)  $N = 2^4 = 16$ . There are 16 possible combinations of input bits for a 4-input AND gate.

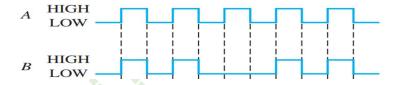

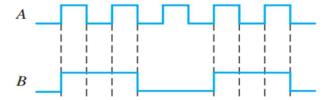

**Example:** If two waveforms, A and B, are applied to the AND gate inputs as in following figure, what is the resulting output waveform?

#### Sol.

The output waveform X is HIGH only when both A and B waveforms are HIGH as shown in the timing diagram.

A and B are both HIGH during these four time intervals; therefore, X is HIGH

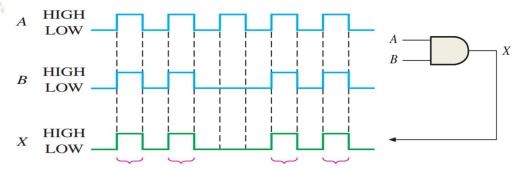

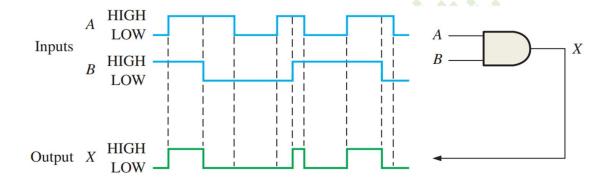

**Example:** For the two input waveforms, A and B, in following figure, show the output waveform with its proper relation to the inputs.

#### Sol.

The output waveform is HIGH only when both of the input waveforms are HIGH as shown in the timing diagram.

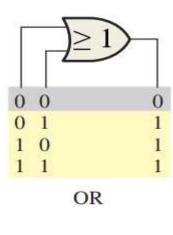

#### 3.4 The OR Gate

The OR gate is another of the basic gates from which all logic functions are constructed. An OR gate has two or more inputs and one output, as indicated by the standard logic symbols in Figure below, where OR gates with two inputs are illustrated.

$$X = A + B$$

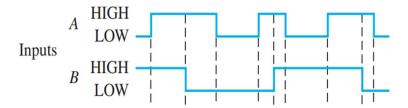

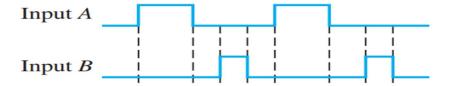

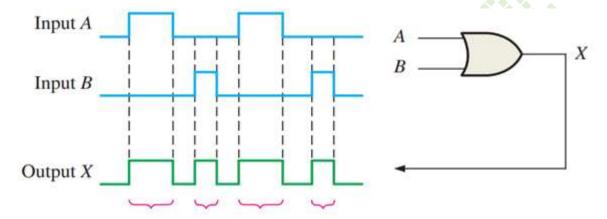

Example: If the two input waveforms, A and B, in following figure are applied to the OR gate, what is the resulting output waveform?

Sol.

The output waveform X of a 2-input OR gate is HIGH when either or both input waveforms are HIGH as shown in the timing diagram. In this case, both input waveforms are never HIGH at the same time.

When either input or both inputs are HIGH, the output is HIGH

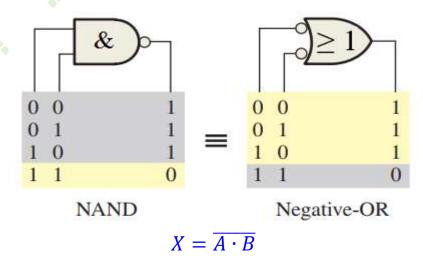

# 3.5 The NAND Gate

The NAND gate is a popular logic element because it can be used as a universal gate; that is, NAND gates can be used in combination to perform the AND, OR, and inverter operations.

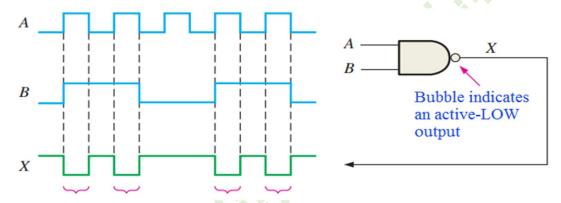

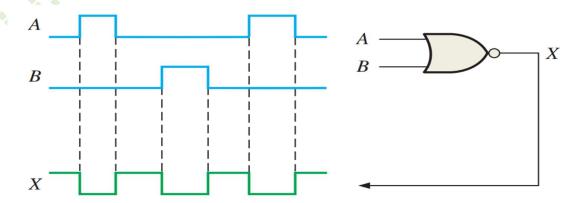

**Example:** If the two waveforms A and B shown in following figure are applied to the NAND gate inputs, determine the resulting output waveform?

#### Sol.

Output waveform X is LOW only during the four time intervals when both input waveforms A and B are HIGH as shown in the timing diagram.

A and B are both HIGH during these four time intervals; therefore, X is LOW.

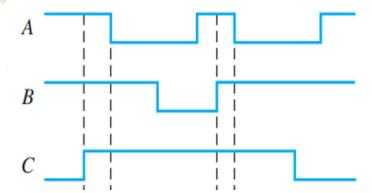

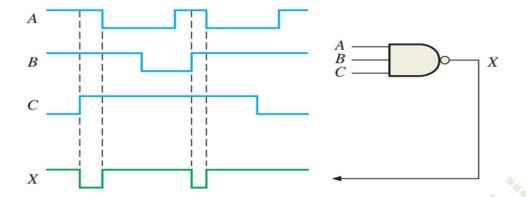

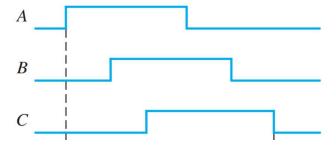

**Example:** Show the output waveform for the 3-input NAND gate in following figure with its proper time relationship to the inputs?

#### Sol.

The output waveform X is LOW only when all three input waveforms are HIGH as shown in the timing diagram.

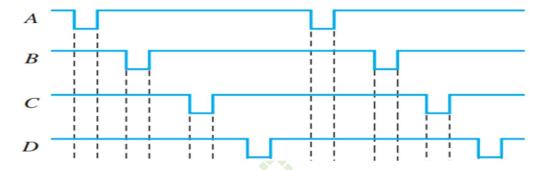

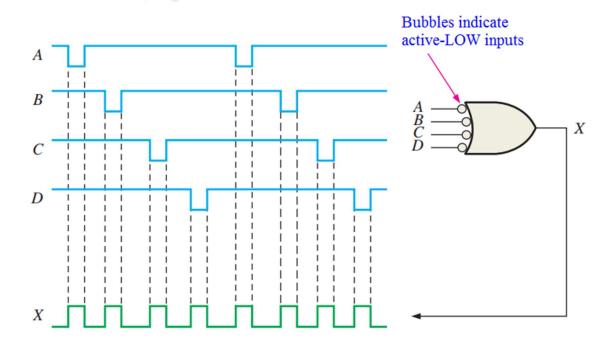

**Example:** For the 4-input NAND gate in the following figure, operating as a negative-OR gate, determine the output with respect to the inputs?

# Sol.

The output waveform X is HIGH any time an input waveform is LOW as shown in the timing diagram.

#### 3.6 The NOR Gate

The NOR gate, like the NAND gate, is a useful logic element because it can also be used as a universal gate; that is, NOR gates can be used in combination to perform the AND, OR, and inverter operations.

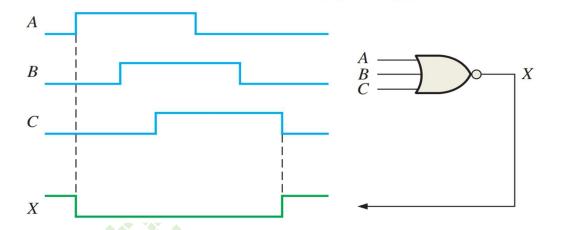

**Example:** If the two waveforms shown in following figure are applied to a NOR gate, what is the resulting output waveform?

Sol.

Whenever any input of the NOR gate is HIGH, the output is LOW as shown by the output waveform X in the timing diagram.

**Example:** If Show the output waveform for the 3-input NOR gate in following figure with the proper time relation to the inputs?

### Sol.

The output X is LOW when any input is HIGH as shown by the output waveform X in the timing diagram.

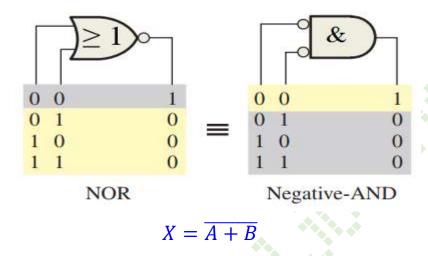

**Example:** A device is needed to indicate when two LOW levels occur simultaneously on its inputs and to produce a HIGH output as an indication. Specify the device?

#### Sol.

A 2-input NOR gate operating as a negative-AND gate is required to produce a HIGH output when both inputs are LOW, as shown in following figure

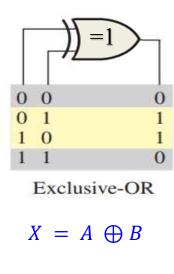

#### 3.7 The Exclusive-OR Gate

The XOR gate has two or more inputs. For two inputs XOR, the output is similar to that from the OR gate except it is "0" when both inputs are "1". In general, an XOR gate gives an output value of "1" when there is an odd number of 1's on the inputs to the gate.

| Truth table for a 3-input XOR gate |       |          |        |  |  |

|------------------------------------|-------|----------|--------|--|--|

|                                    | Input |          | Output |  |  |

| A                                  | В     | <u>C</u> | X      |  |  |

|                                    | •     |          |        |  |  |

| 0                                  | 0     | 0        | 0      |  |  |

| 0                                  | 0     | 1        | 1      |  |  |

| 0                                  | 1     | 0        | 1      |  |  |

| 0                                  | 1     | 1        | 0      |  |  |

| 1                                  | 0     | 0        | 1      |  |  |

| 1                                  | 0     | 1        | 0      |  |  |

| 1                                  | 1     | 0        | 0      |  |  |

| 1                                  | 1     | 1        | 1      |  |  |

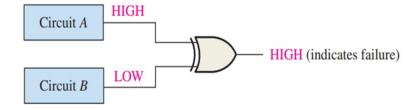

**Example:** A certain system contains two identical circuits operating in parallel. As long as both are operating properly, the outputs of both circuits are always the same. If one of the circuits fails, the outputs will be at opposite levels at some time. Devise a way to monitor and detect that a failure has occurred in one of the circuits?

#### Sol.

The outputs of the circuits are connected to the inputs of an XOR gate as shown in following figure. A failure in either one of the circuits produces differing outputs, which cause the XOR inputs to be at opposite levels. This condition produces a HIGH on the output of the XOR gate, indicating a failure in one of the circuits.

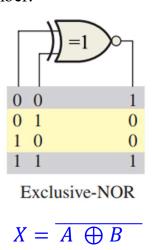

#### 3.8 The Exclusive-NOR Gate

The output in this gate is equivalent to inverting the output from the XOR gate. In general, an XNOR gate gives an output value of "1" when there is an even number.

| Truth table for a 3-input NOR gate |   |          |        |  |  |  |

|------------------------------------|---|----------|--------|--|--|--|

| Input                              |   | t        | Output |  |  |  |

| A                                  | В | <u>C</u> | X      |  |  |  |

|                                    |   |          |        |  |  |  |

| 0                                  | 0 | 0        | 1      |  |  |  |

| 0                                  | 0 | 1        | 0      |  |  |  |

| 0                                  | 1 | 0        | 0      |  |  |  |

| 0                                  | 1 | 1        | 1      |  |  |  |

| 1                                  | 0 | 0        | 0      |  |  |  |

| 1                                  | 0 | 1        | 1      |  |  |  |

| 1                                  | 1 | 0        | 1      |  |  |  |

| 1                                  | 1 | 1        | 0      |  |  |  |

|                                    |   |          |        |  |  |  |

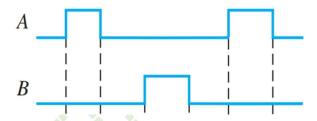

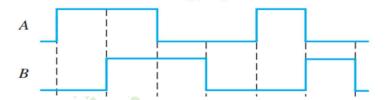

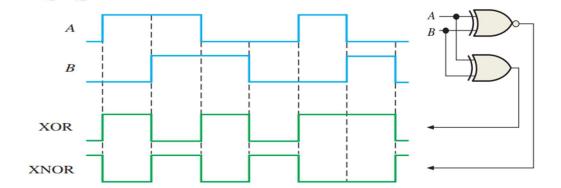

Example: Determine the output waveforms for the XOR gate and for the XNOR gate, given the input waveforms, A and B, in following figure?

Sol.

**Notice** that the **XOR** output is HIGH only when both inputs are at opposite levels. **Notice** that the **XNOR** output is HIGH only when both inputs are the same.

# 3.9 Summary of Logic Gates

| Logic Function           | Symbol & Notation | Boolean Notation            | Explanation                                                                                                                      |

|--------------------------|-------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| NOT                      | A — — — —         | $X = \overline{A}$          | The inverter NOT simply accepts an input and <b>outputs the opposite</b> .                                                       |

| AND                      | A B AB            | $X = A \cdot B$             | All inputs must be positive (1) before the output is positive (1 or ON)                                                          |

| NAND<br>"Not AND         | A                 | $X = \overline{A \cdot B}$  | Same as AND, but the outcome is the inverse (NOT).  So, perform AND first, then apply NOT to the output.                         |

| OR                       | A A+B             | X = A + B                   | At least one input must be positive (1) to give a positive output (1 or ON).  All inputs could also be positive.                 |

| NOR<br>Not OR            | A DO- A+B         | $X = \overline{A + B}$      | Same as OR, but the outcome is the inverse (NOT).  So, perform OR first, then apply NOT to the output.                           |

| XOR<br>eXclusive OR      | A → B             | $X = A \oplus B$            | Only one input can be positive (1) to give a positive output (1 or ON).  If both are positive, the output is negative (0 or OFF) |

| XNOR<br>eXclusive Not OI | A → A⊕B           | $X = \overline{A \oplus B}$ | All inputs must be the same (either high or low) for a positive output (1).  Otherwise, the output is negative (0 or OFF)        |